八十五學年度 **電機工程學** 系(所) 乙 組碩士班研究生入學考試 和自 電子學 科號 3002 共 3 頁第 1 頁 \*請在試卷【答案卷】內作答

- 1. For the high-input-resistance metering circuit of Fig. 1 using a 1-mA meter movement, 5% (a) find the value of the resistor R such that full-scale reading is obtained for  $v_1$ = 2.5V. 5% (b) If the meter resistor is 50 $\Omega$ , what is the OP amp output voltage at half scale?

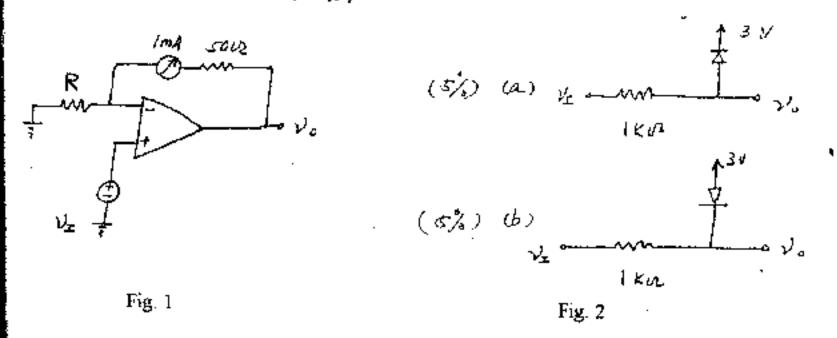

- Sketch the transfer characteristic v<sub>0</sub> verse v<sub>i</sub> for the limiter circuits shown in Fig. 2

All diodes begin conducting at a forward voltage drop of 0.5V and display voltages drops of 0.7V when fully conducting. (10 %)

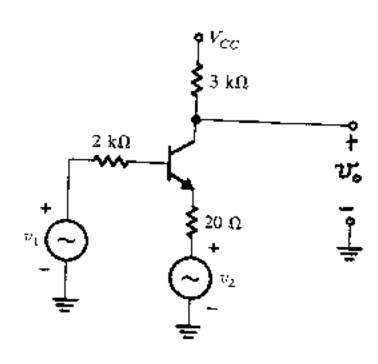

3. For the following circuit, find  $W_{\rm s}$  in terms of  $U_{\rm t}$  and  $U_{\rm t}$ . The BJT has  $\beta=100$ ,  $r_{\rm te}=1{\rm k}\Omega$ , or  $r_{\rm e}=10\Omega$  (12%).

|    | 八十五學年度 | 電機工程學_系           | (所) | <u>Z</u>    |   | 組碩士班研究生入學考試   |

|----|--------|-------------------|-----|-------------|---|---------------|

| 科目 | 電子學    | 科號 <u>3002</u> _共 | 3   | <b>真第</b> 2 | 筫 | *請在試卷【答案卷】內作答 |

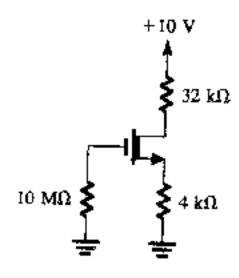

4 Analyze the following to determine  $I_{D}$  and  $V_{D}$ . The depletion MOSFET has  $V_{+} = -1v$  and  $K = 0.5 \text{ mA/V}^{2}$  (8%).

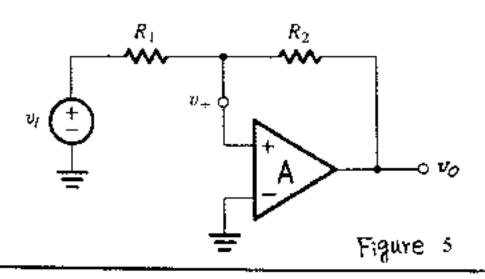

- A circuit as shown in figure 5 consists of an ideal operational amplifier A, two resistors  $R_1$  and  $R_2$ , and an input signal source  $v_i$ . Assuming that the operational amplifier is powered by  $\pm V_m$  and its output voltage limits are 1V short of the power rail voltages.

- (a) Analyze the circuit behaviors, and plot the voltage transfer characteristics ( $v_0$  versus  $v_1$ ), indicate all the voltages intersecting both  $v_0$  and  $v_1$  axes in terms of  $V_m$ ,  $R_1$ , and  $R_2$ . (8%)

- (b) From the results obtained in part (a), can you identify and give the common well-known name of the circuit? (2%)

- (c) In your analysis in part (a), can you use the virtual ground concept which is often employed in analyzing circuits that contain operational amplifiers? Your answer must give supporting reasoning. (4%)

- (d) If the circuit is intended to be used as a waveform shaping circuit, that is to shape a sinusoidal wave of v<sub>1</sub> = A<sub>m</sub> sin ωt into a square wave at output v<sub>0</sub> with an amplitude of B<sub>m</sub>, what is the maximum of B<sub>m</sub>? And what is the design constraint on the relation among the parameters B<sub>m</sub>, R<sub>1</sub>, R<sub>2</sub>, and A<sub>m</sub>? (6%)

八十五學年度

電機工程學

系(所)

乙

組碩士班研究生入學者試

科目

電子學

科號

3002 共 3 寅第 3 頁 \*請在試卷【答案卷】內作答

- Explain why an emitter resistor can effectively increase the output resistance of a commonemitter amplifier. Please also find the enlargement factor for this effect. (10%)

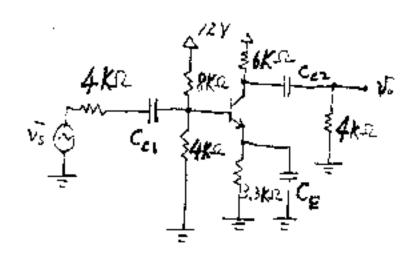

- 7. Estimate the high-band corner frequency  $\omega_{\rm H}$  for the following circuit. Assume that  $\beta = 100$  and  $c_{\rm g} = 10c_{\rm p} = 1$  pF. (10%)

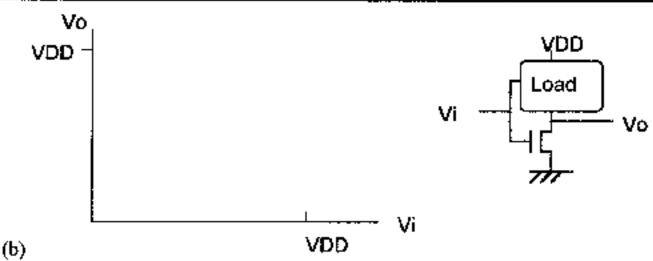

- 8. Compare the inverters implemented in CMOS, depletion NMOS load (Dep.-NMOS), and Enhancement NMOS (Enh-NMOS) load with "equal" dimensions.

- 9% (a) Fill the blanks with simple comments or with correct connections and

11% (b) draw the voltage transfer characteristics of those 3 inverters, mark  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$ ,  $V_{IL}$  at each curve.

| (a)                                     | CMOS Inverter | DepNMOS   | EnhNMOS |

|-----------------------------------------|---------------|-----------|---------|

| Power Dissipations                      |               |           |         |

| Draw connections<br>(include substrate) |               | <br><br>% | U VDD   |