科目:<u>電子學</u>科號:<u>4102/3802</u> 共<u>3</u> 頁第<u>) 頁 \*請在試卷【答案卷】內作</u>

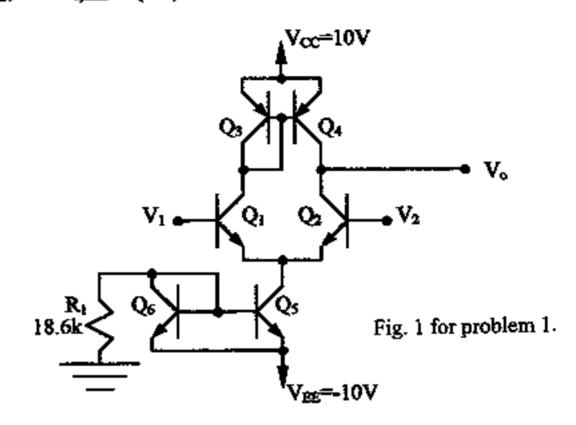

- In the differential amplifier circuit as shown, all transistors are matched with parameters β=100, V<sub>A</sub>=100 V, V<sub>EE(co)</sub>=0.7 V, V<sub>CE,col</sub>=0.3 V.

- (1) Calculate the following parameters: (10%)

- a. gm value of Q1 and Q2

- b. differential voltage gain V<sub>0</sub>/(V<sub>1</sub>-V<sub>2</sub>)

- c. differential input resistance

- (2) Find the minimum input common mode voltage V<sub>CM,min</sub> and the output voltage swing V<sub>0,min</sub>, and V<sub>0,max</sub>. (9%)

- A common emitter amplifier was found to have a single-time-constant high frequency response with mid-band voltage gain of 40 dB and upper 3-dB frequency of 100 KHZ.

- (1) Sketch the Bode plot for the voltage gain |A| (3%)

(2) Find |A|dB for frequencies at 400 KHZ and 4 MHz. (5%)

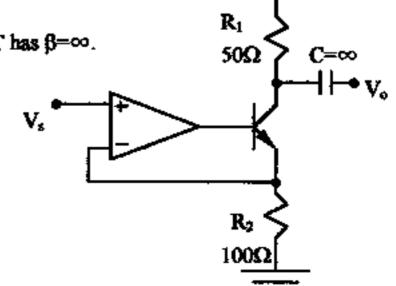

- In the circuit, the op-amp is ideal and the BJT has β=∞.

- What is the feedback topology?

Explain your reason.

- (2) Find the voltage gain V<sub>s</sub>V<sub>s</sub>.

- (3) Find the power dissipation on the BJT when V<sub>5</sub>=2 V.

(8%)

$V_{\infty} = 10V$

Fig. 2 for problem 3

科目:<u>電子學</u>科號:<u>4102/3802</u> 共<u>3</u>頁第<u>2</u>頁 <u>\*請在試卷【答案卷】內作答</u>

- 4. A lightly doped pn diode is used for light detector with N<sub>a</sub>=2x10<sup>14</sup>cm<sup>-3</sup> and N<sub>d</sub>=1x10<sup>16</sup> cm<sup>-3</sup>. Assume the depletion region widths in the p region and the n region are W<sub>p</sub> and W<sub>n</sub>, respectively.

- (a) What is  $W_p / W_n?(5\%)$

- (b) Find the maximum W<sub>p</sub> and W<sub>n</sub> that can be obtained if the junction breaks down at reverse bias voltage of 30V and assume the critical field for junction breakdown is 1x10° V/cm. (5%)

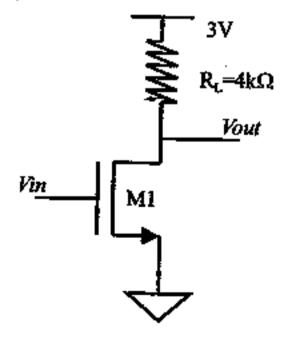

- For a common-source stage with a resistor load is shown in Fig. 3 below. Assume k<sub>p</sub>=100μA/V<sup>2</sup>, W=20μm, L=1μm, V<sub>T</sub>=1V and neglect channel length modulation effect for M1.

- (a) Find the input bias range within which M1 is in saturation (5%)

- (b) What is the maximum small-signal voltage gain of this circuit? (5%)

- (c) Propose changes in the circuit parameters so the input bias range can be increased.(5%)

- (d) Replace M1 with a BJT, Q1 with Is=1x10<sup>-15</sup>A (neglect base current). Estimate the input bias range within which Q1 is in forward-active region. (5%) (FYI: ln2=0.69, ln3=1.1, ln5=1.6, ln7=1.9,ln10=2.3)

Fig.3 for problem 5.

科目:<u>電子學</u>科號:<u>4102/3802</u> 共<u>3</u>頁第<u>3</u>頁 <u>\*請在試卷【答案卷】內作答</u>

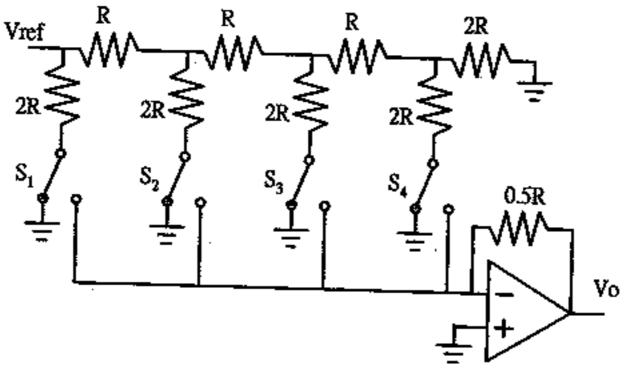

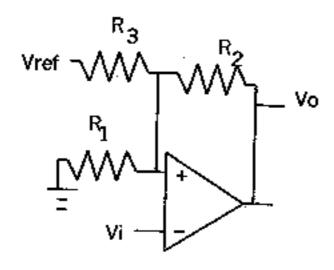

## For Fig. 4 below,

- (a) Draw the Input-output plot with explanations. 5%

- (b) What is this circuit's name? 5%

- (c) What are the limitations/constraints of this circuit? 5%

Fig. 4 for problem 6.

- 7. In Fig. 5, the saturated outputs for the ideal Op Amp are +10V and -10V,

- (a) If Vref =0V, draw the Vi-Vo plot with explanations. (5%)

- (b) If Vref =5V, draw the Vi-Vo plot with explanations. (5%)

- (c) How do you get precise output level by using a resistor and two Zener diodes? 5%

- (d)Also draw the Vi-Vo plot in (c) and show the values of the output levels with

$$V_{Z,reverse} = 5V$$

and  $V_{Z, forward} = 0.5V (5\%)$

Fig. 5 for problem 7