## 國立清華大學命題紙

科目\_\_\_\_\_\_ 至 學 \_\_\_\_\_科目代碼 \_\_\_\_ 9904 \_\_\_\_ 共 \_\_3 \_\_頁第 \_\_1 \_\_頁 \*請在試卷 【答案卷】 內作答

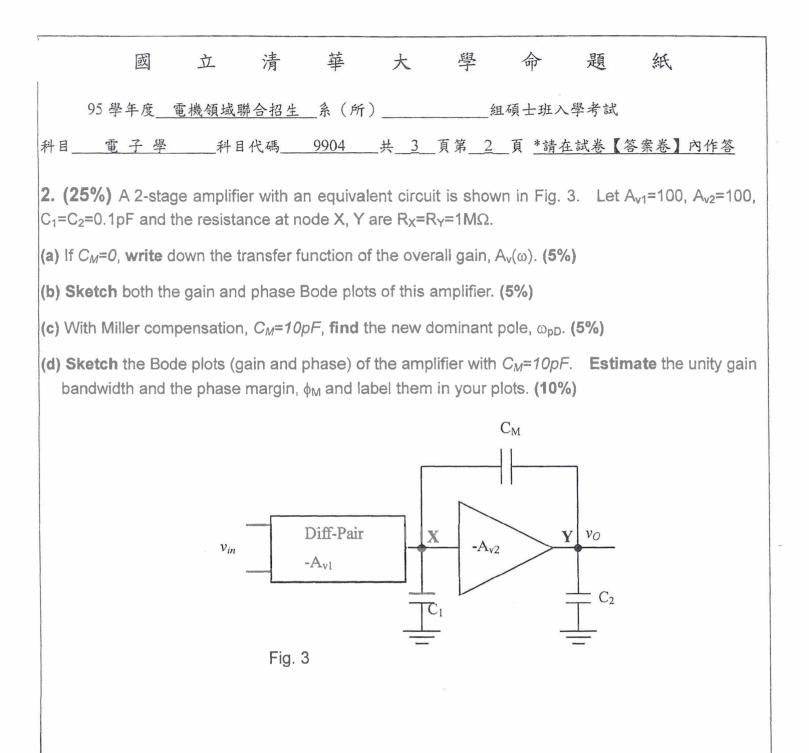

1. (25%) Please mark 1A(a), 1A(b), ..., 1A(e), 1B(a), and 1B(b), respectively, in top of your answers.

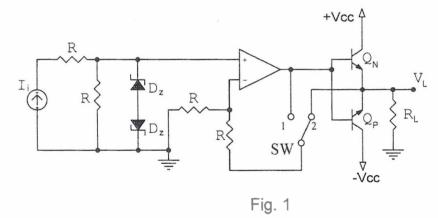

(1A) In a typical driver circuit as shown in Fig. 1, the zener diodes  $D_z$  are ideal with zener voltage  $V_z = 5.3$  V and forward cut-in voltage  $V_{\gamma} = 0.7$  V. The operational amplifier is ideal too. The BJTs,  $Q_N$  and  $Q_P$ , can be modeled by  $|V_{BE(on)}| = 0.7$  V. The power supply is  $V_{CC} = 15$  V. The resistors are  $R = 1 \ k\Omega$  and  $R_L = 10 \ \Omega$ . The switch SW can be selected either in position 1 or position 2. A current signal I<sub>i</sub> with average I<sub>av</sub> and peak-to-peak I<sub>pp</sub> is applied to the input.

(a) When SW is at position 2, find the small signal gain  $V_1/I_i$ . (3%)

(Case 1) When  $I_i$  is a saw-tooth waveform with  $I_{av} = 0$  and  $I_{pp} = 10$  mA,

(b) plot the waveform of  $V_L$  for SW being at position 1. (3%)

(c) plot the waveform of  $V_L$  for SW being at position 2. (3%)

(Case 2) When  $I_i$  is a saw-tooth waveform with  $I_{av} = 0$  and  $I_{pp} = 20$  mA,

- (d) plot the waveform of  $V_L$  for SW being at position 1. (3%)

- (e) plot the waveform of  $V_L$  for SW being at position 2. (3%)

**Note**: Be sure to properly indicate the voltage values in your plots.

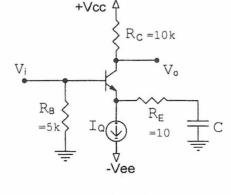

(1B) A Si-BJT with  $\beta$  = 100 and  $r_o = \infty$  is used to make a common emitter amplifier biased by a constant current source as shown in Fig. 2. The capacitance C is very large.

(a) Sketch the small signal equivalent circuit for this amplifier using hybrid- $\pi$ -model. (4%)

(b) If a voltage gain of  $V_o/V_i = -200$  is desired, find the value of  $I_Q$  and the input resistance  $R_{in}$ .

(6%)

Fig. 2

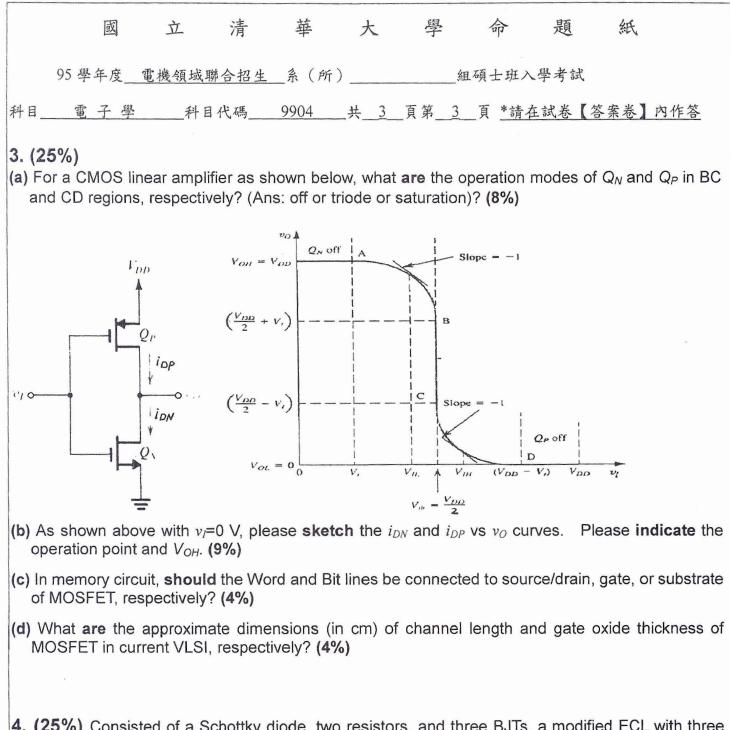

- **4.** (25%) Consisted of a Schottky diode, two resistors, and three BJTs, a modified ECL with three inputs *A*, *B*, *V*<sub>R</sub> and an output *C* is described as follows. Two primary inputs *A*, *B* and a reference voltage *V*<sub>R</sub> are connected to the bases of BJT Q2, Q1, and Q3, respectively; All the emitters of BJT Q1, Q2, and Q3 are connected to node *E*, and the first resistor  $R_E$  are wired between node E and ground; Both the collectors of BJT Q1 and Q2 are wired to power supply *Vcc*, while the collector of BJT Q3 is the output *C*. The Schottky diode and the second resistor  $R_c$  are wired in parallel between power supply *Vcc* and output *C*.

- (a) Please draw this modified ECL circuit. (10%)

- (b) Write the output function C in terms of inputs A and B with brief explanation. (6%)

- (c) Find voltages of  $V_R$ , logic-0 and logic-1 in terms of Vcc and  $V\gamma$ , where  $V\gamma$  is the turn-on voltage of the Schottky diode. (9%)